The University of Hong Kong

## COMP4801 Final Year Project

# **Final Report**

## Simulation of Simple Computer System for Teaching

Wong Yin Lok 3035094933

13 April 2017

### Abstract

This Final Year Project – Simulation of Simple Computer System for Teaching is about the development of a simulator for the purpose of enhancing teaching and learning experience in the Computer Science course COMP2120 Computer Organization. This project has completed with the delivery of two simulation components in one simulator program, one for CPU simulation and the other for cache memory simulation. Comparing to the simulators that have been developed for this course, the deliverable from this project offers an equally comprehensive yet more intuitive to use simulator program with added features. Users will be able to define their custom instructions and see the simulation result via the dynamic display, together with the cache memory simulation, users will consolidate their relevant knowledge to a practical level and at their own pace.

### Acknowledgement

This project is supervised by Dr. K. P. Chan from the Department of Computer Science at the University of Hong Kong.

### **Table of Content**

| Background                                                         | 5  |

|--------------------------------------------------------------------|----|

| Objective                                                          | 6  |

| Previous Work                                                      | 6  |

| Scope and Deliverables                                             | 8  |

| Instruction Definition                                             | 8  |

| Graphical Simulation                                               | 12 |

| Cache Simulation                                                   | 15 |

| Miscellaneous                                                      | 17 |

| Methodology                                                        | 17 |

| CPU Simulation                                                     | 17 |

| Cache Memory Simulation                                            | 25 |

| Experiments and Results                                            | 27 |

| Testing and Evaluations                                            | 30 |

| Error Prevention in Instruction Definition                         | 30 |

| Error Prevention in Simulation Display and Cache Memory Simulation | 31 |

| Miscellaneous                                                      | 35 |

| Conclusion and Future Works                                        | 37 |

| References                                                         | 38 |

| Appendix 1                                                         | 39 |

| Appendix 2                                                         | 43 |

### **List of Figures**

| Figure 1    | 5  |

|-------------|----|

| Figure 2    | 5  |

| Figure 3    | 6  |

| Figure 4    | 7  |

| Figure 5    | 8  |

| Figure 6    | 9  |

| Figure 7    | 9  |

| Figure 8.1  | 10 |

| Figure 8.2  | 10 |

| Figure 8.3  | 10 |

| Figure 9    | 12 |

| Figure 10   | 13 |

| Figure 11   | 13 |

| Figure 12.1 | 15 |

| Figure 12.2 | 16 |

| Figure 13   | 18 |

| Figure 14   | 20 |

| Figure 15   | 21 |

| Figure 16   | 24 |

| Figure 17   | 25 |

| Figure 18   | 26 |

| Figure 19   | 28 |

| Figure 20   | 29 |

| Figure 21 | 29 |

|-----------|----|

| Figure 22 | 32 |

| Figure 23 | 32 |

| Figure 24 | 32 |

| Figure 25 | 32 |

| Figure 26 | 33 |

| Figure 27 | 33 |

| Figure 28 | 33 |

| Figure 29 | 34 |

| Figure 30 | 34 |

| Figure 31 | 34 |

| Figure 32 | 36 |

| Figure 33 | 36 |

|           |    |

### List of Tables

| Table 1 | 11 |

|---------|----|

| Table 2 |    |

| Table 3 | 21 |

| Table 4 | 30 |

|         |    |

### Background

Computer organization and architecture is the basic knowledge to be learnt, if not mastered, in Computer Science and related studies. The study of computer organization explores the fundamental functions performed by any computer system – to move data around and perform simple arithmetic operations. These two simple functions, however, are not very intuitive to be programmed. As the operations are carried out by the CPU, which identifies only bits of 1 and 0, all the instructions to be programmed have to be translated to segments of numbers - known as the assembly code - to indicate specific operations and data location according to a scheme referred to as the instruction set. Figure 1 shows an example programme of CPU execution.

|     | LD    | P0,R4    | 0000: | 0600ff04 | 0000003c |

|-----|-------|----------|-------|----------|----------|

|     | LD    | P1,R1    | 0008: | 0600ff01 | 00000040 |

|     | MOV   | R1,R2    | 0010: | 05010002 |          |

|     | LD    | P2,R3    | 0014: | 0600ff03 | 00000044 |

| L:  | ADD   | R4,R1,R4 | 001C: | 00040104 |          |

|     | ADD   | R1,R2,R1 | 0020: | 00010201 |          |

|     | SUB   | R3,R1,R5 | 0024: | 01030105 |          |

|     | BNZ   | L        | 0028: | 0802ff00 | 000001c  |

|     | ST    | R4,P     | 0030: | 0704ff00 | 00000048 |

|     | HLT   |          | 0038: | 09000000 |          |

| P0: | .WORD | 0        | 003C: | 00000000 |          |

| P1: | .WORD | 1        | 0040: | 0000001  |          |

| P2: | .WORD | A        | 0044: | 0000000a |          |

| P:  | .WORD |          | 0048: | 00000000 |          |

Figure 1. example programme of CPU execution

The instruction set is a set of mnemonic instructions, including common ones like ADD, SUB and MOV that is performed by the CPU. The disassembled, pseudo code is written in a form like "ADD R4,R1,R4" while the actual assembly code perceived by the CPU is like series of hexadecimal numbers corresponding to different operations and registers or memory addresses.

Simply understanding the disassembled code but not being able to translate them into hexadecimal assembly codes is not enough. Students do need to understand the translation.

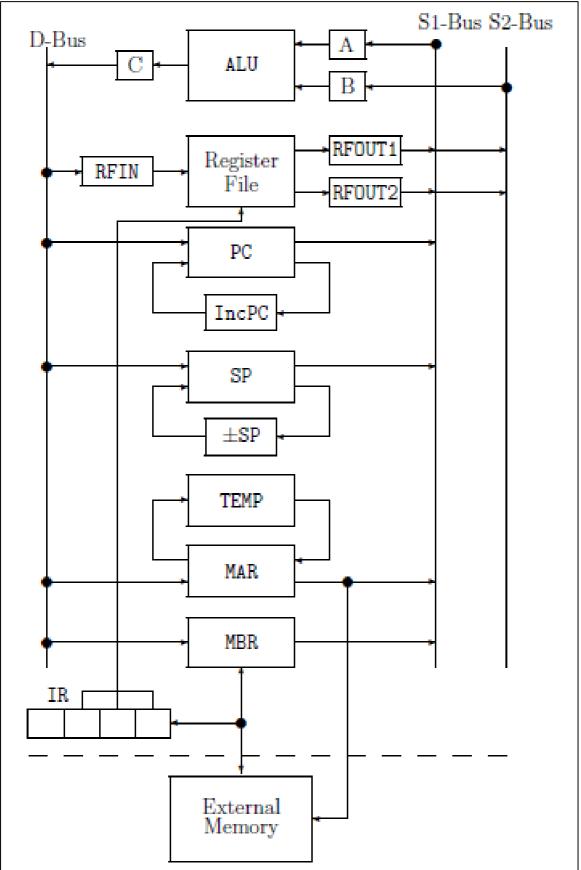

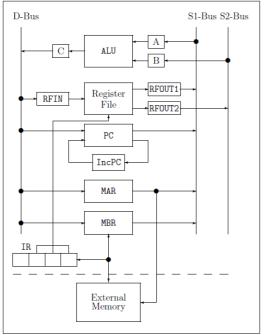

Figure 2. CPU architecture used in COMP2120

This means students have to write code in series of digits and try to keep track of the actual data movements and operations based on these abstract lines of hexadecimal operation codes. Not only is the code written in hexadecimal numbers difficult to follow, the thorough understanding of actual CPU operations is not reflected in the code.

Figure 2 shows an example CPU architecture used in the Computer Science course Computer Organization. In actual CPU operations, each operation code in the instruction set, e.g. ADD and SUB, is implemented by a series of interactions between the CPU components. For example, in an ADD operation, internal register data are read from the RF ports and moved via the system buses, then followed by some other actions involving other CPU

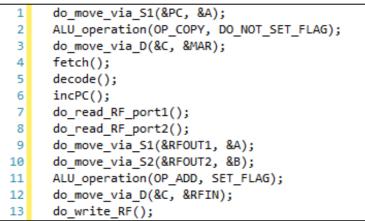

components, as shown in figure 3. These details are not shown or practiced when students write codes, since the programme codes will only be lines of instruction code like "00040104"

representing "ADD R4,R1,R4" without disclosing the actions of the CPU components required for that single line of code.

In addition, memory cache replacement can be а confusing process in which different slots of the memory cache are swapped out and replaced by new memory content. Memory caching is process of reading the comparably slow memory into fast-access CPU cache. While the number of slots and the size of the memory cache are fixed, the replacements come in

Figure 3. sample "ADD" definition translated from the implementation in C of the simulator<sup>1</sup> currently used in COMP2120

different orders, targeting different slots every time depending on the replacement scheme. This is, as what we see with CPU operations, difficult to follow without proper visualization. To help students better picture the above details, the idea of a graphical simulator was born.

### Objective

The grand objective of this project is to improve teaching and learning in the course Computer Organization regarding the working mechanism of CPU and cache memory. More specifically, in the CPU simulation, it is to help students visualize and understand the detailed operations inside the CPU for different instructions; in cache memory simulation, it is to help students understand the logic of different memory replacement scheme by visualizing the update of memory content.

### **Previous Work**

This project is not new. Last year, another student took up this project as his Final Year Project. But the Java simulator built in that project turned out to be more of a step by step "video player" of execution statements loaded from some configuration files. The CPU simulation would read in a file containing the programme executions and display the execution results of every line of code one after another in a description panel controlled by the user, and the memory panel would display the update of memory in respective memory slots. Figure 4 shows a screenshot of the simulator from the project last year.

<sup>&</sup>lt;sup>1</sup> sim.cc. Hong Kong: HKU COMP2120

Figure 4. screenshot of the simulator from previous project, captured from the corresponding final report<sup>2</sup>

While the memory simulation might be dynamic and representable enough, the CPU simulation was lacking in strengthening students' understanding of the underlying CPU actions that are performed behind each instruction.

The graphical display of the simulator would highlight the CPU component involved according to the sequence of program executions. However, the relationship between individual CPU actions and the corresponding instruction was not clearly demonstrated. In addition, visualization alone has only minimal effect to the understanding of behind-the-scene CPU operations, but thorough understanding could hardly be achieved just by watching tens of seconds of animation.

The key is to introduce the element of practical implementation, so as to install knowledge via solid practice and hands-on experience. This current project, therefore, basically started all over again from scratch in order to introduce the new element of custom instruction definition, which will be mentioned in later parts of this report and largely deviated from the approach adopted in the previous project. For cache memory simulation, despite the fact that it was probably catered fairly in the project last year, its development in this current project depended heavily on the CPU simulation where the source codes of the two simulations interconnect. Thus, in the end, no code from the previous project was taken as reference or recycled throughout the course of this project.

There is, however, another simulator<sup>3</sup> of an older origin, written in C and has been used as the tool in the course for several years, from that this project has taken reference from. This simulator, despite being comprehensive in functionalities, shares the same downsides as the other simulator.

<sup>&</sup>lt;sup>2</sup> Wong, Jing Hing(Kent). FINAL REPORT TOPIC: COMPUTER SYSTEM SIMULATOR. Hong Kong: 2015

<sup>&</sup>lt;sup>3</sup> sim.cc. Hong Kong: HKU COMP2120

Figure 5. screenshot of running the simulation from the simulator currently used in COMP2120

As shown in figure 5, the simulator is a command-linebased program that runs on the terminal interface with text output. It is rigid and inflexible in that all instructions used in the programme are predefined in the simulator logic and what users do are only supplying an external configuration file and then reading the text output from the console window.

The simulator from the final year project last year attempted to improve on this simulator by providing more vivid graphical content, yet the core of the problem remains that students do not easily gain a thorough understanding to the underlying hardware-level operations by simply reading from the simulation output.

This current project tackles specifically on this problem by introducing new features, while taking reference from the implementation logics of the standard operations defined in this simulator currently used in the course.

### **Scope and Deliverables**

The final deliverable is a Java program including two simulation components, namely the CPU simulation and the cache memory simulation. Java was chosen because of the hopeful reusability of previous codes and the platform independent nature of the compiled program which can then be distributed to students as an educational tool. While simulation of any of these two system components can involve a wide range of relevant concepts and complex implementation details, the scope of this project is carefully controlled in order to streamline the deliverable and make it focused on its educational purpose.

#### **Instruction Definition**

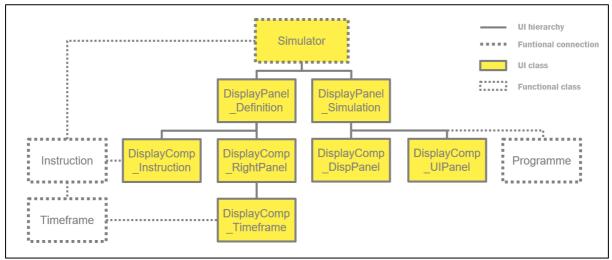

To begin with, the CPU simulation contains two major parts implemented in two separate display panel.

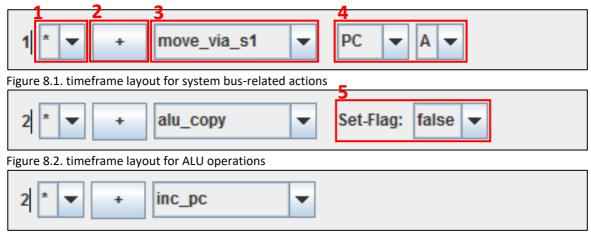

The first part is mnemonic instruction definition, and its completed interface is shown in figure 6. As stated in previous sections, the objective of the CPU simulation is to allow users to learn and better understand the actual operations happening inside the CPU, via practical hands-on experience rather than merely watching the graphical display run. In this part of the simulation, users will be able to define the implementations of custom instructions.

| Simple Co                                                    | mputer    | System Sim | nulatio | n | – 🗆 X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------|-----------|------------|---------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| struction D                                                  | efinition | n Simulat  | tion    |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 01                                                           | - /       | ADD        | 00      | < | 1 * • • move_via_s1 • PC • A •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 02                                                           | -         | SUB        | 01      | > |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 03                                                           | - [       | AND        | 02      | > | 2 * • Alu_copy • Set-Flag: false •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 04                                                           | -         | OR         | 03      | > | 2 + + inc_pc +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 05                                                           | -         | NOT        | 04      | > |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 06                                                           | - [       | MOV        | 05      | > | 3 * • + move_via_d • C • MAR •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 07                                                           | -         | LD         | 06      | > | 4 + read_instruction +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 08                                                           | -         | ST         | 07      | > |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 09                                                           | -         | BR         | 80      | > | 5 * 🕶 + read_rf_port1 💌                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 10                                                           | -         | PUSH       | 09      | > | 5 + read_rf_port2 +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11                                                           | -         | POP        | 10      | > |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12                                                           | -         | HLT        | 11      | > | 6 • • • move_via_s1 • RF1 • A •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                              |           |            |         |   | 6 + • + move_via_s2 • RF2 • B •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                              |           |            |         |   | 7 * • + alu_add • Set-Flag: true •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| +                                                            |           |            |         |   | 8 Torregulate the second secon |

| Addressing Mode identifying bits:<br>Direct f Displacement e |           |            |         |   | 9 × • + write_rf •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Import Export + - Save Help                                  |           |            |         |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

As seen from figure 6, the input of the mnemonic names is on the left of the panel where users will add and type in the name of the mnemonic instructions that they want to define, with the hexadecimal operation code for that instruction. For the sake of maintaining the program logic and reducing its complexity and thus the possibility of errors, the number of instructions that can be defined is capped at a maximum of 16,

Figure 6. interface for mnemonic mapping of the CPU simulation

which should be more than enough for writing general programmes.

At the start of the simulator program, the left of the panel will be initialized with one single entry of empty textfields and buttons, shown in figure 7.

Figure 7. dissection of an empty instruction entry

Section labelled number 1 in figure 7 is the graphical index of the instruction entry. The button labelled numbered 2 is the removal button that is not enabled for the first entry but on all others for removal of the particular instruction. This suggests that the simulator works with at least one instruction definition and cannot function with no instruction input. Textfields numbered 3 and 4 are respectively the entry for the mnemonic symbol of the instruction and the hexadecimal operation code. The length of the mnemonic symbol is capped at six characters while that of the opcode is capped at two numeric characters due to the fact that the opcode is signified by two bits in an eight-bit instruction word in hexadecimal assembly code. After the input of the mnemonic symbol is captured, the opcode textfield and the button on the right labelled 5 will be enabled to allow the expansion of the right panel for configuring hardware-level actions that the instruction will perform. This is to ensure that every instruction will get its mnemonic symbol and opcode defined properly.

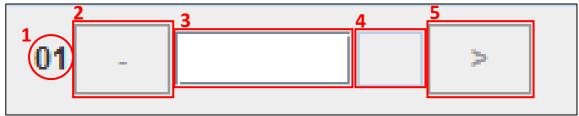

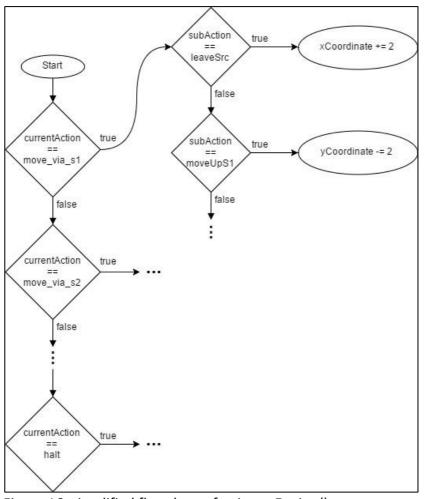

On the right of the CPU simulation panel as shown in figure 6, corresponding CPU actions that implement the desired function of the custom instruction can be added and selected in the drop-down boxes. One rectangular entry represents an action to be performed in an execution timeframe of the CPU. There are three types of layout for the action entries, as shown in figure 8.1, 8.2 and 8.3.

Figure 8.3. timeframe layout for all other actions

Sections labelled number 1 to 3 in figure 8.1 are commonly seen in all three types of layout. The drop-down box numbered 1 determines the addressing mode of that particular CPU action, which will be discussed later. The button numbered 2 adds an additional CPU action to the current timeframe for the purpose of parallelizing the operations, which will also be discussed later in this section. The drop-down box numbered 3 determines the CPU action to be performed, the list of CPU actions - a total of twenty-two different actions - supported by this simulator is shown as table 1 and will be discussed further in this section. The two drop-down boxes in section number 4 in figure 8.1 is specific to entries when the CPU action selected in drop-down box number 3 is related to data movement via the system buses, i.e. "move\_via\_s1", "move\_via\_s2" and "move\_via\_d", where the first drop-down box on the left specifies the data source while the right box specifies the destination of the data movement.

Figure 8.2 shows the layout when the CPU action involves operations by the ALU unit, e.g. "alu\_add" and "alu\_not". The section labelled number 5 determines whether the result of the ALU operation should update the zero-flag on which the "branch" action depends. If Set-Flag is true, when the result of the ALU operation is not zero, zero-flag is set to 0, otherwise set to 1; if Set-Flag is false, the result of the ALU operation will not update the zero-flag.

Figure 8.3 shows the layout when the CPU action involves operations other than the two types mentioned above. There will be no supplementary information needed for these other actions. Note that these differences in the information needed for different CPU actions are important, not only to properly implement the desired behaviour of the action in the simulation, but also in the import and export functionalities provided by the simulator, which will be covered later in this section.

| <b>Elementary Actions</b> |

|---------------------------|

| move_via_s1               |

| move_via_s2               |

| move_via_d                |

| inc_pc                    |

| read_rf_port1             |

| read_rf_port2             |

| write_rf                  |

| alu_add                   |

| alu_sub                   |

| alu_and                   |

| alu_or                    |

| alu_not                   |

| alu_copy                  |

| read_instruction          |

| read_memory               |

| write_memory              |

| branch                    |

| dec_dp                    |

| inc_sp                    |

| mar_to_temp               |

| temp_to_mar               |

| halt                      |

Table 1. list of hardwarelevel actions supported by this simulator

Besides the add button mentioned above, i.e. button numbered 2 in figure 8.1, as seen from figure 6, there is another add button alongside other buttons near the bottom of the right of the simulation panel. This difference in functionality of this additional add button with all the other add buttons within the timeframe entries is worth noting as well as the significance of the index numbers in the timeframes. For example as seen from figure 8.2 and 8.3, the two entries, as part of the definition for the custom instruction "ADD" as shown in figure 6, share the same graphical index number. These are designed for parallelization. As different CPU operations involve the use of different resources, there are times when the operations are independent to each other in terms of both time and resources that they can be parallelized instead of having to proceed in a serial manner. In this case, when "alu\_copy" is being performed, "inc\_pc" can be performed simultaneously without causing any abnormality of the programme logic or resource conflict. Hence, after the user have selected "alu\_copy" in timeframe 2, the user can then click the add button within the entry to initialize another parallel action within the same timeframe. If the user hopes to initialize a new timeframe in a sequential manner, e.g. from index 1 proceeding to index 2, the user can then click the add button at the bottom.

The "-" button removes only the last timeframe with all its action entries, for the sake of implementation simplicity - as the maintenance of the proper ordering of the arraylist of the entries with some sharing the same graphical index is counter-intuitive

enough, not to mention the need to cater for removal of items in the middle of the list. That means if the last timeframe, for example, three action entries all with the same graphical index, the three entries will all be removed when the removal button is clicked.

The "Save" button, together with the "+" and "-" button at the bottom, will only be enabled when there is an instruction expanded for action configuration, i.e. when the button numbered 5 in figure 7 of the corresponding instruction shows "<", indicating that it is currently being edited. The "Save" button is used to save the custom definition for the use of CPU simulation. The meaning of "saving the definition" will be explained in the Methodology section.

Similar to the limit in instructions, there is a limit of thirty action entries that can be added for each instruction, regardless of the index number, parallel or sequential. This number should be more than enough for definition of standard instructions.

After an instruction is configured and saved, after are some other actions the user can perform before going into the actual simulation. For example, by clicking the rectangular "+" button at the bottom left, the user can then add another instruction entry for a maximum total of sixteen instructions.

The textfields under "Addressing Mode identifying bits" specifies the hexadecimal bits that represent the use of different addressing mode. This simulator supports by default two addressing modes, with "f" representing the use of direct addressing and "e" representing the use of displacement addressing. These bits correspond to selection from the drop-down box numbered 1 shown in figure 8.1.

If the user chooses "\*" from the drop-down box, that particular action will be executed regardless of which addressing mode the current instruction is in, as specified in the programme input, which will be covered in the next subsection Graphical Simulation. If the user chooses "f" or "e", that particular action will only be executed when the addressing mode specified is in the corresponding direct or displacement addressing.

There are at last the import and export buttons. This simulator provides no internal storage mechanism but instead provides the import and export function in consideration of possible distribution and submission of the definition text files in the course being easier than each of the students having their own saved state of the simulator.

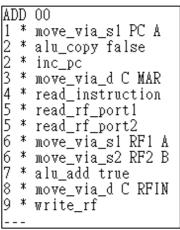

After the definition is saved, the user can click the export button to export a definition text file containing the definition of all saved instructions. A section of a sample text file is shown in figure 9, while a complete definition file containing 12 standard instructions can be viewed in appendix 1.

Figure 9. extract of sample definition text file

The exported definition will be in .txt format. And the definitions saved in the text file can be loaded to the simulator by clicking the import button and selecting the text file.

Figure 9 provides a clue to the format of the definition file. For each instruction definition, the syntax of the file begins with a line containing the instruction mnemonic symbol and the two-bits opcode, separated by space. Following the first line, the actions in the instruction are specified by lines starting with the timeframe index, followed by the addressing mode identifying bit, the hardware-level action string, then the optional information depending on the action, all separated by space. At the end of the instruction, a line of three dashes and another empty line is used to signal the end of the definition and the start of another definition can then begin.

The definition text file can be exported or composed manually. But upon manually construction, the syntax of the content should follow the-above-mentioned. Otherwise, the import may fail. Further description about handling mal-formatted import is covered in section Testing and Evaluation.

#### **Graphical Simulation**

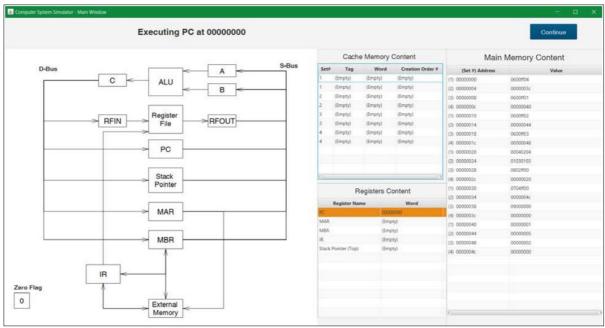

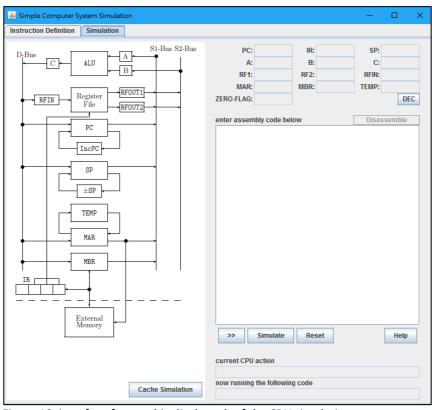

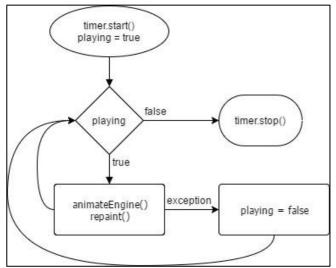

The second part of the CPU simulation is animated graphical display. This graphical display is essentially a video player that shows data movements and operations in the CPU. Figure 10 shows the completed interface of the graphical display.

The simulator provides a large text field for users to type in their programme in hexadecimal assembly codes. The operation codes are mapped to their corresponding mnemonic instructions in the previous stage. This programme input serves as the basis for the graphical display to run.

An example assembly programme in hexadecimal codes is shown in figure 11. Note that there are certain syntax that the

Figure 10. interface for graphic display tab of the CPU simulation

programme has to follow in order for the simulator to correctly load and decode the code lines.

| enter assembly code below | Disassemble |

|---------------------------|-------------|

| 00000: 01010101           |             |

| 00004: 01020202           |             |

| 00008: 0600ff01 00000020  |             |

| 00010: 0600e103 00000024  |             |

| 00018: 11000000           |             |

| 00020: 00000004           |             |

| 00024: 00000024           |             |

| 00028: 00000ffe           |             |

|                           |             |

|                           |             |

|                           |             |

|                           |             |

|                           |             |

|                           |             |

|                           |             |

|                           |             |

|                           |             |

|                           |             |

|                           |             |

Every line of code should begin a with a 5 bits address. The entire programme is essentially assigning different data into different memory address slots. Following the 5 bits has to be a colon and a space. Then comes the content to be assigned to the address. The content can take two data different formats, one being a oneword instruction/data, the other being a two-word instruction/data. The former takes in an 8 bits data string while the latter takes in a 8 bits data string, followed by a space separator, followed by another 8 bits data string. These syntax rule has to be strictly followed, otherwise, an error

Figure 11. sample programme input

message will pop up and the simulation will not begin. Details on handling mal-formed input will be discussed in the section Testing and Evaluation.

When the "Simulate" button is clicked, there will be colored points, alongside the data content in small text, representing data signals, moving on the CPU image to indicate data movement. Relevant CPU hardware components on the path, e.g. PC and MAR, will have content update which will be shown in the respective description fields at the top right beside the display.

There is a "DEC" button at the top right near the hardware description fields, which serves the purpose of changing the numeric base of the display content. As data in the simulation is represented in hexadecimal numbers, which is not intuitive to read, the simulator offers another decimal base of representation. The bases of numeric representation can be changed back and forth between decimal and hexadecimal anytime upon the user's discretion. Note that the change to decimal base is only to provide the user with an optional, and more convenient visual representation, and is independent of the data content concerned. With this said, all description fields - except PC, MAR and SP, which are always containing address data in hexadecimal representation, and the ZERO-FLAG which can only be in 1 or 0 - will have their bases changed when the button is clicked, even when address data in hexadecimal get into the temporary C register.

When the "Simulate" button is clicked, the simulation begins by reading the content in address "00000" as specified in the programme input. The "Simulate" button then shows "Pause", and when clicked, will pause the simulation to allow the user to read and digest the information on the graphical display or the descriptions fields on the right. After clicking "Pause" and the simulation paused, the button shows "Simulate" again and can resume the simulation when clicked again.

The double-arrow button beside the "Simulate" button controls the speed of the simulation animation. There are three different speeds for the simulation that the user can switch from one to another using the speed button during the simulation. This design is to allow users to quickly go through the simulated actions which have been seen repeatedly under many occasions that users are already familiar with. The speed will be reset automatically to the default pace upon entering a new line of instruction to ensure that no instruction simulation is skipped unintentionally.

The "Reset" button stops the simulation if it is running and reset all the description fields and internal variables used in the simulation.

The two textfields at the bottom right are descriptions to the current simulation status, providing textual hints for users to follow the simulation. The description field on top displays one or more of the twenty-two elementary CPU actions listed in table 1 that are currently running, and the bottom field shows the eight-bits instruction word that is being executed together with the address containing that word.

As students are required to programme with custom instruction sets in the course, this part of the simulation allows them to test their very own implementations and enhance understanding of the principle. However, it is not possible for the simulation to support definitions of any unseen operation, because after all, the functions of all the custom instructions are limited to the combination of the hardware-level actions are listed in table 1.

| <b>Guaranteed Instructions</b> |

|--------------------------------|

| ADD                            |

| SUB                            |

| AND                            |

| OR                             |

| NOT                            |

| MOV                            |

| LD                             |

| ST                             |

| BR/BZ/BNZ                      |

| PUSH                           |

| РОР                            |

| HLT                            |

Table 2. Guaranteed instructiondefinitions by this simulator

For example, for operations that require the use of ALU unit to perform simple arithmetic like addition and subtraction, the ALU operations will have to be pre-defined by the simulation system. Therefore, this simulator will only guarantee that the definitions of twelve standard instructions can be achieved, as listed in table 2, with possibility of defining other novel instructions. The sample definition of the standard instructions is attached in appendix 1.

Note that the "HLT" instruction is not a genuine instruction in a sense that it does not require the step of instruction fetch, its functionality of halting the running simulation is simply by the power of the single "halt" action in the definition. This "halt" action is designed only for the purpose of the simulator. As in real-life CPU execution, the

cycle is essentially an infinite loop that does not stop at any point. In contrary to that, the simulation here better has a finite stop to signal the user of a completion. Therefore, this "halt" action and thus "HLT" instruction are added.

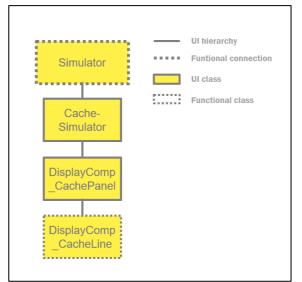

### **Cache Simulation**

Figure 12.1 interface for cache memory simulation on Windows

The other major component of the final deliverable is cache memory simulation. With limited size in the cache, there are different schemes to determine how to access and replace the cache content. The simulation will allow the user to choose from two most commonly-used schemes covered in COMP2120, namely FIFO(First-In-First-Out) and LRU(Least-Recently-Used). For write policy, both write through and write back will be supported. As cache configuration, 2-way associative mapping is used with a total of four cache sets. These choices allow simple and easy graphical representation on one hand, and on the other, are some of the most commonly used options in real-life cache memory.

Figure 12.1 shows the completed interface of the cache simulation window on Windows, while figure 12.2 shows that on macOS. The major difference between the two interface lies in the difference of the color scheme. Different colors are used to signify different cache sets, however, during development, it is found that there are problems updating the memory content on Windows if the colors used

have an alpha value less than 100, as in the implementation on macOS and Linux. Therefore the colors used for Windows environment are changed.

This cache simulation window will show in a separate window beside the panel of CPU simulation when the "Cache Simulation" button on the left in figure 10 is clicked. Note that the "Cache Simulation" button will be disabled when the simulation has begun, meaning that

the cache simulation has to be initialized before then. The same applies to cache replacement algorithm and write policy, which have to be chosen by clicking the corresponding buttons before the simulation begins and cannot be altered during the process.

|                           | Cache Memory Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | N             |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Memory-Cache Mapping      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Memory Conten |

| 2-Way Associative Mappi   | ng                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 00000:        |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 00004:        |