Project Title : TrC-MC: Decentralized Software Transactional Memory for Multi-Multicore Computers -- A word-based STM based on TinySTM 0.9.5.

|

Introduction

The rise of multicore processor architecture has reshaped supercomputing and marked the beginning of a new era.To date, systems researchers are actively looking for promising parallel paradigms that permit future software both ease-of-use and high concurrency to solve this problem. The idea of software-only transactional memory (STM) was popularized in 1995 and has become a heavily reviewed candidate to increase the software-exposed parallelism for scaling with more and more cores. The purpose of this project is to design and implement a new parallel programming paradigm and memory consistency model for simple and efficient multi-threaded programming on multi-core machines.

|

Micro-architecture |

Clock rate |

Cores |

Threads per core |

Threads per package |

Shared cache |

Memory arrangement |

|

IBM Power 7 |

~ 3 GHz |

4 ~ 8 |

4 |

32 Max |

4 MB |

NUMA |

|

Sun Niagara2 |

1.2 ~ 1.6 GHz |

4 ~ 8 |

8 |

64 Max |

4 MB |

NUMA |

|

Intel Westmere |

~ 2 GHz |

4 ~ 8 |

2 |

16 Max |

12 ~ 24 MB |

NUMA |

|

Intel Harpertown |

~ 3 GHz |

2 x 2 |

2 |

8 |

2 x 6 MB |

UMA |

|

AMD Bulldozer |

~ 2 GHz |

2 x 6 ~ 2 x 8 |

1 |

16 Max |

8 MB |

NUMA |

|

AMD Magny-Cours |

~ 3 GHz |

8 modules |

2 per module |

16 Max |

8 MB |

NUMA |

|

Intel Terascale |

~ 4 GHz |

80? |

1? |

80? |

80 x 2 KB |

NUCA |

Project Objectives

The use of locks for synchronization and mutual exclusion among cooperating threads has been known for years. Yet lock-based consistency models have been criticized for poor programmability since they easily lead to deadlocks if not used carefully. Performance is also unsatisfactory as locks may serialize program code that can execute in parallel without data race. In recent years, many researches focused on the use of transactions – a concept originated from database systems – to replace locks for synchronizing multi-threaded programs in a machine with multiple processors. These researches claimed that transactions offer better programmability than locks because deadlocks never occur. They can also improve application performance as multiple threads can read the same shared memory location concurrently. Based on transactions, software transactional memory (STM) was devised to ensure memory consistency among threads in a single machine without special hardware support. Many variants of STM have been proposed for different programming languages, including C, C++, Java and C#.

Yet three drawbacks of STM – namely excessive aborts, coarse granularity of data sharing and conflict detection overhead – can hinder its performance. Moreover, programmers who are used to locks may be reluctant to change their programming style and modify existing application code. Thus we propose a new memory consistency model called trock consistency for multi-core (TrC-MC). It is based on trocks, a new synchronization facility that unifies the behavior of transactions and locks, while compatible to both of them. Applications using locks or transactions can be converted to trocks without major code modification. On one hand, trocks follow the ACID property (atomicity, consistency, isolation and durability) and enable concurrent, optimistic execution of threads as transactions do, hence eliminating any deadlocks in lock-based programs. On the other, TrC-MC can outperform STM through our proposed features, including prioritized contention management, fine-grained data sharing and reduction of conflict detection. TrC-MC can benefit a wide variety of multi-threaded applications, especially those which extensively perform reads on collective data structures like hash maps, lists and arrays.

The key problems solved:

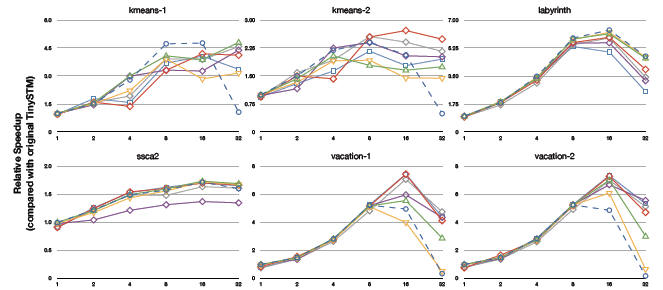

- We identify a current multicore hardware bottleneck, which obstructs STM from scaling in some transactional workloads.

- We extend a distributed-clock STM with two optimization changes, and prove the correctness of the resultant design.

- We evaluate the distributed-clock STM, including our optimizations, with some real world benchmark programs, and recorded huge performance difference.

- We successfully reduced the abort rate of the distributedclock STM to an acceptable level.

|

| Transaction commits and aborts of some TM applications on dual- and qual-core computers |

Publication

-

Kinson Chan and Cho-Li Wang, Optimizing Decentralized Software Transactional Memory for Multi-Multicore Computers, The 17th IEEE International Conference on Parallel and Distributed Systems (ICPADS 2011), Tainan, Taiwan, December 7-9, 2011. (paper) (PPT)

-

Kinson Chan, King Tin Lam, Cho-Li Wang, Adaptive Thread Scheduling Techniques for Improving Scalability of Software Transactional Memory, International Conference on Parallel and Distributed Computing and Networks (PDCN2011), Feb 15-17, 2011, Innsbruck, Austria (pdf)

Reference and Related Work

- Transactional Memory Bibliography

- Shavit, N., Touitou, D. 1995. Software transactional memory. In Proceedings of the 14th ACM Symposium on Principles of Distributed Computing: 204–213

- Software Transactional Memory: Why Is It Only a Research Toy?

Hardware Transactional Memory

- IBM moved transactional memory into BlueGene/Q.

- Sun's Rock processor was cancelled when the company was purchased by Oracle

Software Transactional Memory

- TinySTM

- LibCMT

- RSTM (Rochester STM): C/C++

- JVSTM (Java)

- Deuce (Java)

- Multiverse (Java)

- DSTM: Object-based

- DSTM2 (Java)

- JudoSTM (2007)

- RingSTM (2008)

- Intel’s STM

- TokenTM (2008)

- TL2 STM: Transactional Locking II : C/C++

- LSA STM (paper)

- AtomJava

- STM.NET

- Scala-STM (in Scala)

- Akka STM (Java and Scala)

- CCSTM (paper) (2010): open-source

- Global Transactional Memory (GTM) (2009): (paper)

- Adaptive STM (ASTM): (paper) (2005)

- adaptSTM : word-based STM library that is based on a global clock

- InvalSTM (2010) (paper)

More: Last Update: Jan 12, 2012

Contact: Mr. Kinson Chan (kchan@cs.hku.hk) or Dr. Cho-Li Wang (clwang@cs.hku.hk)